# Fakultät für Mathematik und Informatik Lehrgebiet Rechnerarchitektur

Kurs 1608 "Computersysteme I"

Lösungsvorschläge zu den Aufgaben der Nachklausur im SS 2006

(am 16. September 2006)

# Aufgabe 1 Zahlensysteme

(15 Punkte)

Zeigen oder widerlegen Sie algebraisch die Korrektheit der folgenden Gleichungen:

a)

$$X_0 X_1 \vee X_1 X_2 = \overline{\overline{X_0}} \ \overline{\overline{X_1}} \vee \overline{\overline{X_1}} \ \overline{\overline{X_2}}$$

$$\overline{\overline{X_0}} \ \overline{X_1} \lor \overline{X_1} \ \overline{X_2} = (X_0 \lor X_1)(X_1 \lor X_2)$$

$$= X_0 X_2 \lor X_1 \neq X_0 X_1 \lor X_1 X_2$$

Die Gleichung ist falsch.

(3)

b)

$$\overline{X_1 \lor X_1 \lor X_1 \lor X_1} \lor X_1 \Leftrightarrow 1 = X_1$$

$$\overline{X_1 \lor X_1 \lor X_1 \lor X_1} \lor X_1 \lor X_1 \Leftrightarrow 1$$

$$= \overline{0 \lor X_1 \lor X_1} \lor X_1 = \overline{X_1} \lor X_1 \lor X_1$$

$$= 0 \lor X_1 = X_1$$

Die Gleichung ist richtig.

(3)

c)

$$\overline{X_0 X_1 \vee X_3} \ \overline{\overline{X_0} \vee X_2} = \overline{X_2} X_1 X_0 \overline{X_3}$$

$$\overline{X_0 X_1 \vee X_3} \overline{\overline{X_0} \vee X_2} = \overline{X_0 X_1} \overline{X_3} X_0 \overline{X_2} = (\overline{X_0} \vee \overline{X_1}) \overline{X_3} X_0 \overline{X_2}

= \overline{X_0} \overline{X_3} X_0 \overline{X_2} \vee \overline{X_1} \overline{X_3} X_0 \overline{X_2} = \overline{X_1} \overline{X_3} X_0 \overline{X_2}$$

Die Gleichung ist falsch.

d)  $X_0 \leftrightarrow X_1 = X_0 \lor X_1 \lor X_0 X_1$

$$X_0 \longleftrightarrow X_1 = X_0 \overline{X_1} \vee \overline{X_0} X_1$$

$$\neq X_0 \vee X_1 \vee X_0 X_1 = X_0 \vee X_1 = X_0 X_1 \vee X_0 \overline{X_1} \vee \overline{X_0} X_1$$

Die Gleichung ist falsch.

(3)

e)

$$X_0 X_1 \vee X_0 \overline{X_1} X_2 = X_0 X_1 \vee X_0 X_2$$

$$X_0 X_1 \vee X_0 \overline{X_1} X_2 = X_0 (X_1 \vee \overline{X_1} X_2) = X_0 (X_1 \vee X_2)$$

=  $X_0 X_1 \vee X_0 X_2$

Die Gleichung ist richtig.

(3)

Im Kurstext haben Sie neben dem Dezimalsystem mit der Basis 10 auch das Binärsystem mit Basis 2 sowie die Umrechnung zwischen diesen beiden Systemen kennen gelernt. Das von den Babyloniern entwickelte Sexagesimalsystem arbeitet mit der Basis 60 und findet sich auch heute noch in vielen Anwendungsgebieten, wie z.B. bei der Angabe geographischer Längen und Breiten oder bei der Zeitmessung (Eine Stunde besteht aus 60 Minuten, eine Minute aus 60 Sekunden.).

Ein Kalenderjahr besteht gemäß dem gregorianischen Kalender aus  $31556952_{10}$  Sekunden. Stellen Sie diese Zahl im Sexagesimalsystem dar, indem Sie die einzelnen Ziffern durch Semikolon getrennt im Dezimalsystem angeben (Beispiel:  $125_{10} = 2;5_{60}$ ).

```

60^{0} = 1

60^{1} = 60 (60s entsprechen 1 Minute)

60^{2} = 3600 (3600s entsprechen 1 Stunde)

60^{3} = 216000 (216000s entsprechen 2,5 Tage)

60^{4} = 12960000 (12960000s entsprechen 150 Tage)

```

31556952 / 12960000 = 2 Rest 5636952 5636952 / 216000 = 26 Rest 20952 20952 / 3600 = 5 Rest 2952 2952 / 60 = 49 Rest 12

Folglich gitt:

$31556952_{10} = 2;26;5;49;12_{60}$

#### Ergänzende Eriäuterung:

Das Kalenderjahr dauert gemäß dem Gregorianischen Kalender

```

365 Tage (= 2 * 150 Tage + 26 * 2,5 Tage),

5 Stunden,

49 Minuten und

12 Sekunden.

```

Die letzten drei Ziffern der sexagesimalen Darstellung finden sich offensichtlich bei der Angabe dieser Dauer wieder.

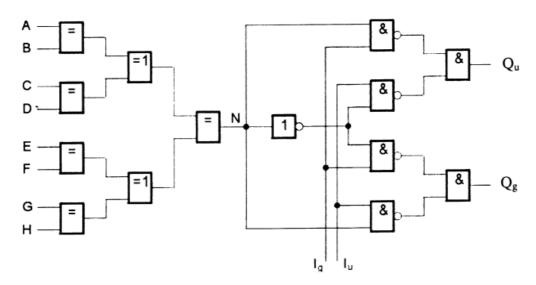

# Aufgabe 3 Analyse eines TTL-Bausteins (15 Punkte)

Analysieren Sie das in der folgenden Abbildung gezeigte Schaltnetz des TTL-Bausteins SN74180!

a) Minimieren Sie die Funktionsgleichungen der Ausgänge  $Q_g$  und  $Q_u$  unter Verwendung von Karnaugh-Diagrammen

Aus dem Schaltbild folgt für Qg:

$\begin{array}{l} Q_g = \overline{N \ I_u} \wedge \overline{\overline{N} \ I_g} = (\overline{N} \vee \overline{I_u}) \wedge (N \vee \overline{I_g}) = \overline{N} \ \overline{I_g} \vee N \ \overline{I_u} \vee \overline{I_u} \overline{I_g} \\ \text{Die Übertragung in das Karnaugh-Diagramm ergibt:} \end{array}$

Und wir erhalten:  $Q_0 = \overline{N} \overline{I_0} \vee \overline{N} \overline{I_0}$

Aus dem Schaltbild folgt für Qu:

$Q_u = \overline{N} \ \overline{l_g} \wedge \overline{\overline{N}} \ \overline{l_u} = (\overline{N} \vee \overline{l_g}) \wedge (\overline{N} \vee \overline{l_u}) = \overline{N} \ \overline{l_u} \vee \overline{N} \ \overline{l_g} \vee \overline{l_g} \ \overline{l_u}$ Die Übertragung in das Karnaugh-Diagramm ergibt:

Und wir erhalten:  $Q_u = \overline{N} \overline{I_u} \vee N \overline{I_g}$

b) Stellen Sie das boolesche (logische) Verhalten in der vorgegebenen Tabelle dar !

| N der 1-Signale von<br>A bis H | l <sub>a</sub> | l <sub>u</sub> | Qg | Q <sub>υ</sub> |  |  |

|--------------------------------|----------------|----------------|----|----------------|--|--|

| 0                              | 0              | 0              | 1  | 1              |  |  |

| 0                              | 0              | 1              | 1  | 0              |  |  |

| 0                              | 1              | 0              | 0  | 1              |  |  |

| · 0                            | 1              | 1              | 0  | 0              |  |  |

| 1                              | 0              | 0              | 1  | 1              |  |  |

| 1                              | 0              | 1              | 0  | 1              |  |  |

| 1                              | 1              | 0              | 1  | 0              |  |  |

| 1                              | 1              | 1              | 0  | 0              |  |  |

c) Welche Aufgabe erfüllt dieser Baustein?

Bei diesem Baustein handelt es sich um einen 9-Bit Paritätsgenerator bzw. 8-Bit Paritätsprüfer.

# Aufgabe 4 Duodezimalsystem-Zähler (20 Punkte)

Im Kurstext wurden neben Zahlen in Dezimaldarstellung auch Binärzahlen verwendet. Auch wenn in der täglichen Praxis überwiegend diese beiden Zahlensysteme sowie Hexadezimalzahlen (Basis 16) zum Einsatz kommen, kann nach dem gleichen Schema zu jeder natürlichen Zahl ein Zahlensystem gebildet werden. In dieser Aufgabe betrachten wir das Duodezimalsystem, welches die Zahl 12 zur Basis hat.

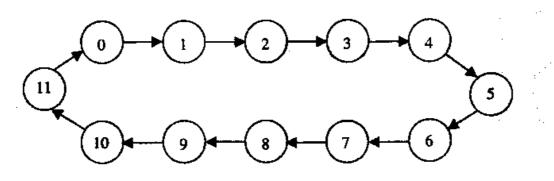

Entwickeln Sie einen Duodezimalzähler, also eine Schaltung, die zyklisch die Ziffern von 0 bis 11 durchzählt, indem Sie die folgenden Teilaufgaben lösen:

#### a) Zeichnen Sie den Zustandsgraphen

b) Erstellen Sie die Zustandsfolgetabelle!

|                |       |       | ţ <sub>n</sub> |       |                |                  |                | 1     | <b>t</b> n + 1 |          |                |

|----------------|-------|-------|----------------|-------|----------------|------------------|----------------|-------|----------------|----------|----------------|

| Q <sub>3</sub> | $Q_2$ | $Q_1$ | Q              | $D_3$ | D <sub>2</sub> | $D_{\mathtt{L}}$ | D <sub>0</sub> | $Q_3$ | Q <sub>2</sub> | $Q_t$    | Q <sub>0</sub> |

| 0              | . 0   | 0     | 0              | 0     | 0              | 0                | 1 <u></u>      | 0     | 0              | 0        | 1              |

| 0              | 0     | 0     | 1              | 0     | : 0            | 1                | 0              | 0     | 0              | <b>1</b> | 0              |

| 0 1            | O     | 1     | 0              | 0 🗆   | 0              | 1                | . ( <b>1</b>   | 0     | 0,             | 1        |                |

| 0              | 0     | 1     | 1              | 0     | 1              | 0                | 0              | · O · | ু 1            | 0        | 0              |

| 0              | 1     | 0     | 0              | 0     | 1              | 0                | 1              | . 0   | ~1             | 0        | 1              |

| 0              | 1     | 0     | 1.             | 0     | 1 7            | - 1              | 0              | . 0   | 1              | 1        | . ee           |

| 0              | 1     | 1     | 0              | 0     | 1              | 1                | 1              | 0     | 1              | 1        | 1              |

| . 0            | 1     | 1     | 1 :            | 1 1   | 0              | 0                | Đ              | 1     | 0              | 0        | 0              |

| 1              | 0     | 0     | 0              | 1     | 0              | 0                | 1              | 1     | . 0            | · 0,     | 10             |

| 1              | 0     | 0     | 1              | 1     | 0              | 1 1              | 0              | 1     | Ð              | 1.       | 0              |

| 1              | 0     | 1     | 0              | 1     | 0              | 1                | 1,             | 1     | 0              | 1        | 1              |

| 1              | 0     | 1     | 1              | 0     | 0              | 0                | 0              | 0     | 0              | 0        | 0              |

(2)

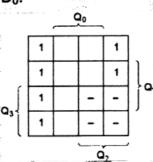

## c) Geben Sie die Übergangsfunktionen in minimaler DNF an!

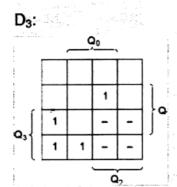

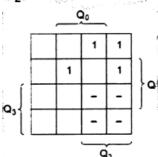

Wir minimieren die Funktionsgleichung für die D-Eingänge. Da die Zustände mit den Werten 12 – 15 nicht vorkommen, werden sie als don't care betrachtet.

$$D_3 = Q_3\overline{Q}_1 \vee Q_3\overline{Q}_0 \vee Q_2Q_1Q_0$$

D<sub>2</sub>:

$$D_2 = Q_2 \overline{Q}_0 \vee Q_2 \overline{Q}_1 \vee \overline{Q}_3 \overline{Q}_2 Q_1 Q_0$$

D<sub>1</sub>:

$$D_1 = \overline{Q}_1 Q_0 \vee Q_1 \overline{Q}_0$$

D<sub>0</sub>:

$$D_0 = \overline{Q}_0$$

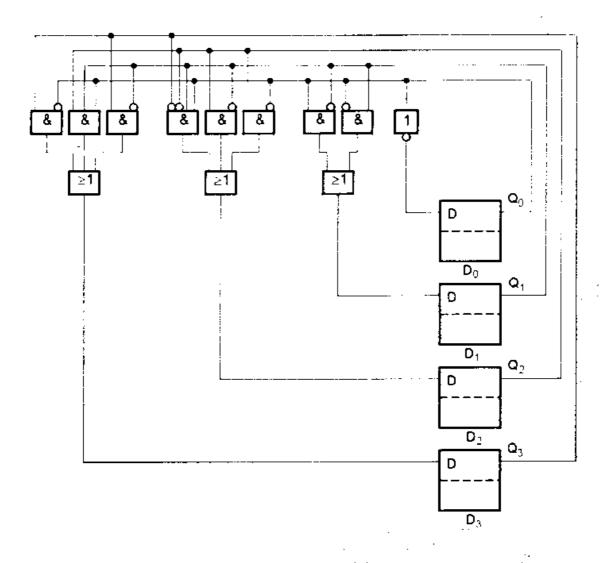

# d) Zeichnen Sie das in den Aufgabenteilen a) – c) entwickette Schaltwerk !

## Aufgabe 5 Komplexe Schaltwerke

(25 Punkte)

Ein digitaler Geschwindigkeitssensor liefert einen 8--Bit Eingangsvektor X als vorzeichenlose Dualzahl. Die Geschwindigkeit wird mit einer Auflösung von 0,25 m/s gemessen. Der Messwert soll zyklisch in km/h umgerechnet werden, die in einem Register Y gespeichert wird. Die Ausgänge dieses Registers sind identisch mit dem Ausgabevektor Y. Die Geschwindigkeit soll mit einer Auflösung von 0,1 km/h als Dualzahl ausgegeben werden.

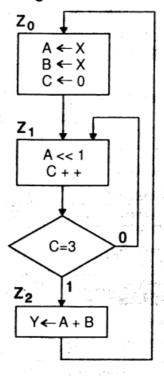

a) Entwerfen Sie ein ASM-Diagramm, in dem lediglich Additions- und 1-Bit Schiebeoperationen verwendet werden.

Zunächst müssen wir den Umrechnungsfaktor ermitteln. Es gilt 0,25 X m/s = 0,1 Y km/h = 0,1 Y 1000m/3600s = Y 0,1m/3,6s Y = 3,6/0,1 \* 0,25 X = 9 X

Um Y mit der gewünschten Auflösung zu berechnen, muss also der Eingangsvektor X mit 9 multipliziert werden. Bei der Anzeige des Ergebnisses muss die letzte Stelle durch ein Komma abgetrennt werden. Man bezeichnet diese Art der Rechnerarithmetik als Festkommadarstellung.

Eine Multiplikation mit 8 erreicht man durch 3-faches Linksschieben. Dabei wird von rechts eine 0 nachgeschoben. Um die erforderliche Multiplikation mit 9 zu erreichen, muss zu diesem Teilergebnis dann nocheinmal X addiert werden.

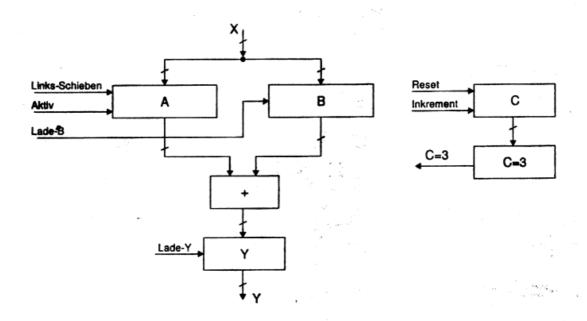

b) Entwerfen Sie das entsprechende Operationswerk.

(10)

### c) Entwerfen Sie ein Steuerwerk mit One-hot Zustandscodierung

Das Steuerwerk erfordert 3 D-Flipflops, die den einzelnen Zuständen zugeordnet werden. Das Rückkopplungsschaltnetz wird durch folgende Funktionen implementiert:

$$D_0 = Q_2 \sqrt{Q_2 Q_1 Q_0}$$

$$D_1 = Q_0 \vee Q_1 \overline{(C=3)}$$

$$D_2 = Q_1 \vee (C = 3)$$

Das Ausgangsschaltnetz des Steuerwerks muss folgende Schaltfunktionen bestimmen:

Links\_Schieben = Q<sub>1</sub>

$Aktiv = Q_0 v Q_1$

$Lade_B = Q_0$

Reset =  $Q_0$

Inkrement = Q<sub>1</sub>

$Lade_Y = Q_2$

(5)

a) Vervollständigen Sie den folgenden Lückentext zur Organisation des Speichersystems eines Computers:

verfügen in Regel über eine vierstufige Heutiae Computer der kommuniziert direkt mit dem Speicherhierarchie . Der Prozessor schnellsten Speicher des Systems, dem L1-Cache. Die Datenübertragung zwischen dem Prozessor und dem L1-Cache erfolgt wortweise. Der L1-Cache befindet sich <u>auf dem Prozessorchip</u> und hat eine typische Größe von 8-64-Kbyte Oft sind für Befehle und \_Daten\_ getrennte L1-Caches vorhanden. Der L2-Cache befindet sich außerhalb des Prozessorchips und wird vorwiegend in CMOS -Technologie gefertigt. Die nächste Stufe bildet der Hauptspeicher, der mit dem L2-Cache blockweise Daten austauscht. Programmteile und Daten, die momentan nicht benötigt werden, befinden sich im üblicherweise mit Hilfe von Festplatten realisierten Hintergrundspeicher und können bei Bedarf den Hauptspeicher geladen werden. (12)

- b) Welche Formen der Speichererweiterung werden im Kurstext genannt?

Speicher kann auf dreierlei Arten erweitert werden:

- 1. Erhöhung der Wortbreite

- Vergrößerung der Speicherkapazität

- 3. Erweiterung von Wortbreite und Speicherkapazität.